## **ACTIVE DELAY LINES, 5-TAP & 10-TAP** THROUGH-HOLE & SURFACE MOUNT

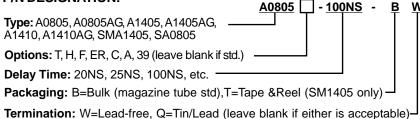

# **A08 SERIES: 8-Pin DIP** A14 SERIES: 14-Pin DIP **SA08 SERIES: 8-Pin SIP SMA14 SERIES: 14-Pin SO**

- ☐ A1405 popular values from stock!

- ☐ Wide selection, 20 1000nS

- □ Choice of 5 or 10 equally spaced taps

- ☐ TTLSchottky interfaced, TTL&DTLcompatible

### **OPTIONS**

- ☐ Opt.T= trailing edge design

- ☐ Opt. F = fast TTL, H = HCMOS, C = FACT

- ☐ Opt.A = auto-insertable design

- $\square$  Opt.ER = -55 to +125°C operating temp.

- $\square$  Opt.39 = -40 to +85°C operating temp.

- ☐ Tighter tolerances, faster rise times

- Military screening

## TOTAL-DELAY TIMES (TD)

20nS, 25nS, 30nS, 40nS, 45nS, 50nS, 60nS, 75nS, 100nS, 125nS, 150nS, 200nS, 250nS, 300nS, 350nS, 400nS, 450nS, **500nS**, 750nS, **1000nS** (popular values listed in bold. Intermediate and extended range values available on special order).

#### **SPECIFICATIONS**

Operating Temp: 0 to 70°C (opt.39= -40 to +85°C, opt.ER= -55 to +125°C)

Rise Time: 4nS max.

Delay Tol: ±2nS or ±5%, whichever greater Tap Tol: ±2nS or 5%, whichever greater Peak Soldering Temp: +230°C

## **CHARACTERISTICS**

| RCD Type | Delay Range  | No. of<br>Taps | Delay<br>per Tap |

|----------|--------------|----------------|------------------|

| A0805    | 20nS - 500nS | 5              | 20% TD           |

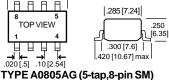

| A0805AG  | 20nS - 500nS | 5              | 20% TD           |

| A1405    | 20nS -1000nS | 5              | 20% TD           |

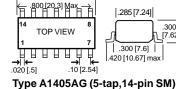

| A1405AG  | 20nS -1000nS | 5              | 20% TD           |

| A1410    | 50nS -1000nS | 10             | 10% TD           |

| A1410AG  | 50nS -1000nS | 10             | 10% TD           |

| SA0805   | 20nS - 500nS | 5              | 20% TD           |

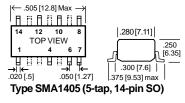

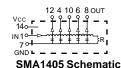

| SMA1405  | 20nS - 250nS | 5              | 20% TD           |

Most popular models are listed in boldface. A1405AG is most popular SM model, A1405 is most popular thru-hole.

## **TEST CONDITIONS @25°C**

- 1.) Input test pulse voltage: 3.2V 2.) Input pulse width: 50nS or 1.2x the

- total delay (whichever is greater)

- 3.) Input rise time: 2.0nS (0.75V to 2.4V)

- 4.) Delay measured at 1.5V on leading edge only with no loads on output (specify opt. T for trailing edge design)

- 5.) Supply Voltage (Vcc): 5V

- 6.) Pulse spacing: 2x pulse width min.

RCD's active delay lines have been designed to provide precise tap delays with all the necessary drive and pick-off circuitry. All inputs/outputs are schottky-type, requiring no additional components to achieve specified delays. Units are 100% inspected. Excellent for applications requiring high delay stability, fast rise times and no jitter, such as memory boards, disk drives, and signal processing. Application Guide available.

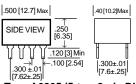

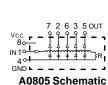

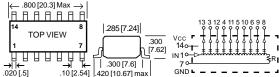

Type A0805 (5-tap, 8-pin DIP)

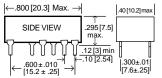

Type A1405 (5-tap,14-pin DIP)

-.800 [20.3] Max. → .40[10.2]max

max.

SIDE VIEW

← .600±.010 [15.2 ± .25]

l l

Type A1410 (10-tap,14-pin DIP)

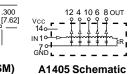

Type A1410AG (10-tap,14-pin SM) A1410 Schematic

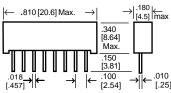

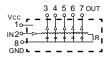

Type SA0805 (5-tap, 8-pin SIP)

SA0805 Schematic

#### P/N DESIGNATION: